|

|

5 months ago | |

|---|---|---|

| .. | ||

| .settings | 6 months ago | |

| Core | 6 months ago | |

| qpc | 6 months ago | |

| .cproject | 6 months ago | |

| .mxproject | 6 months ago | |

| .project | 6 months ago | |

| README.md | 5 months ago | |

| STM32C031C6TX_FLASH.ld | 6 months ago | |

| project Debug.launch | 6 months ago | |

| project Release.launch | 6 months ago | |

| project.ioc | 6 months ago | |

| stm32-nucleo-64_conn.png | 6 months ago | |

| stm32-nucleo-c031c6.webp | 6 months ago | |

README.md

NOTE You must generate the code from the project.ioc file before building the application. If you forget to do this, the following errors will be reported:

fatal error: stm32c0xx_hal.h: No such file or directory 30 | #include "stm32c0xx_hal.h" . . .

Real-Time Example on NUCLEO-C031C6

This example implements the "Periodic-Sporadic" application on the STM32 NUCLEO-C031C6 board (ARM Cortex-M0+). The example demonstrates various real-time preemption scenarios among active objects in the QV kernel. The example requires a logic analyzer.

STM32 NUCLEO-C031C6

Code Organization

stm32c031-cube

| .project // STM32CubeMX project

| project.ioc // STM32CubeMX config (for code generation)

|

+---Core // core application generated by STM32CubeMX

| +---Inc // include files

| +---Src // source files

| | . . .

| | real-time.qm // QM model file for the application

| +---Startup

|

+---qpc // QP/C real-time event framework

| +---include

| +---src

| | +---qf

| | +---qv

| +---ports

| | +---arm-cm

| | | +---qv

| | | | +---gnu

| | . . .

Features Demonstrated

The example QP application consists of 2 periodic tasks (Active Objects) and two sporadic, long-running tasks (Active Objects).

Running the Examples

Setting up a Logic Analyzer

The NUCLEO-C031C6 needs to be conntected to a logic analyzer as shown in the picture below.

CN7 CN10

PD0 PD1 PD3 NC

PD2 PD2 PB8 NC

VDD E5V PB0 NC

PA14 GND -- GND AVDD 5V-USB-CHG

NC NC GND PA3

NC IOREF CH8 -- PA5 PC15

PA13 NRST CH3-- PA6 PB12

NC 3V3 CH2 -- PA7 PB12

PC6 +5V PB0 PB2

GND GND CH7 -- PC7 GND

NC GND PA9 PF3

CH1 -- PC13 VIN PA15 PA8

PC14 NC PB5 PB15

NC PA0 -- CH6 PB4 PB14

PF0 PA1 -- CH5 PB10 PB13

PF1 PA4 -- CH4 PB3 AGND

NC PB1 PA10 PB0

PB11 PA11/PB9 PB6 NC

PA2 PA12/PB8 PB7 NC

The logic analyzer needs to be configured as follows:

- sampling rate: several MHz (e.g., 24MHz)

- trigger: Sporadic (PC.13 on the NUCLEO-C031C6), falling edge

- pre-trigger capture ratio: 10%

Example Logic Analyzer Traces

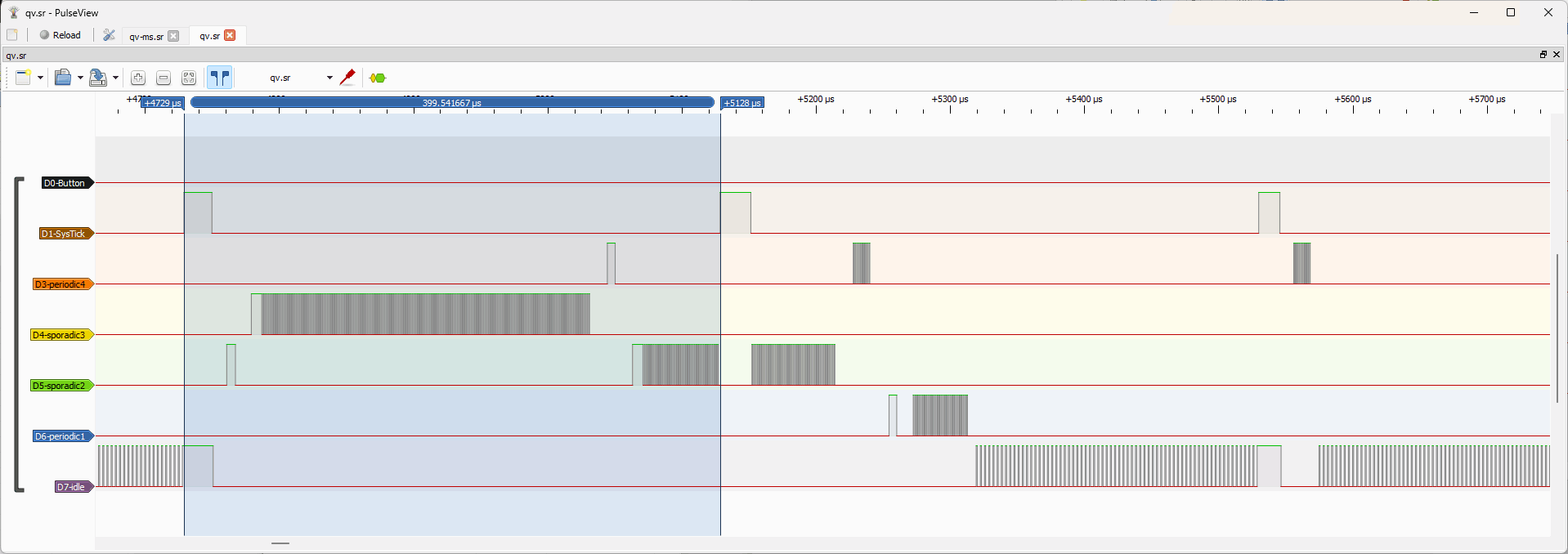

Logic analyzer trace after pressing the button (non-preemptive QV kernel)

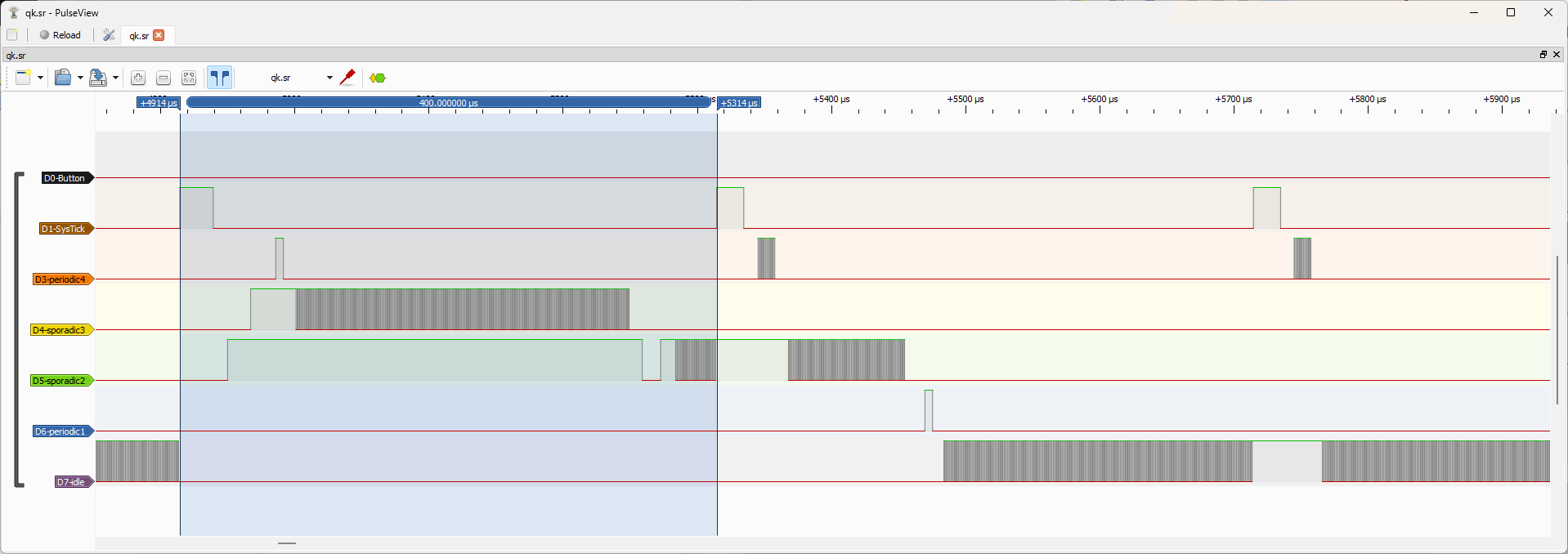

Logic analyzer trace after pressing the button (preemptive QK kernel)

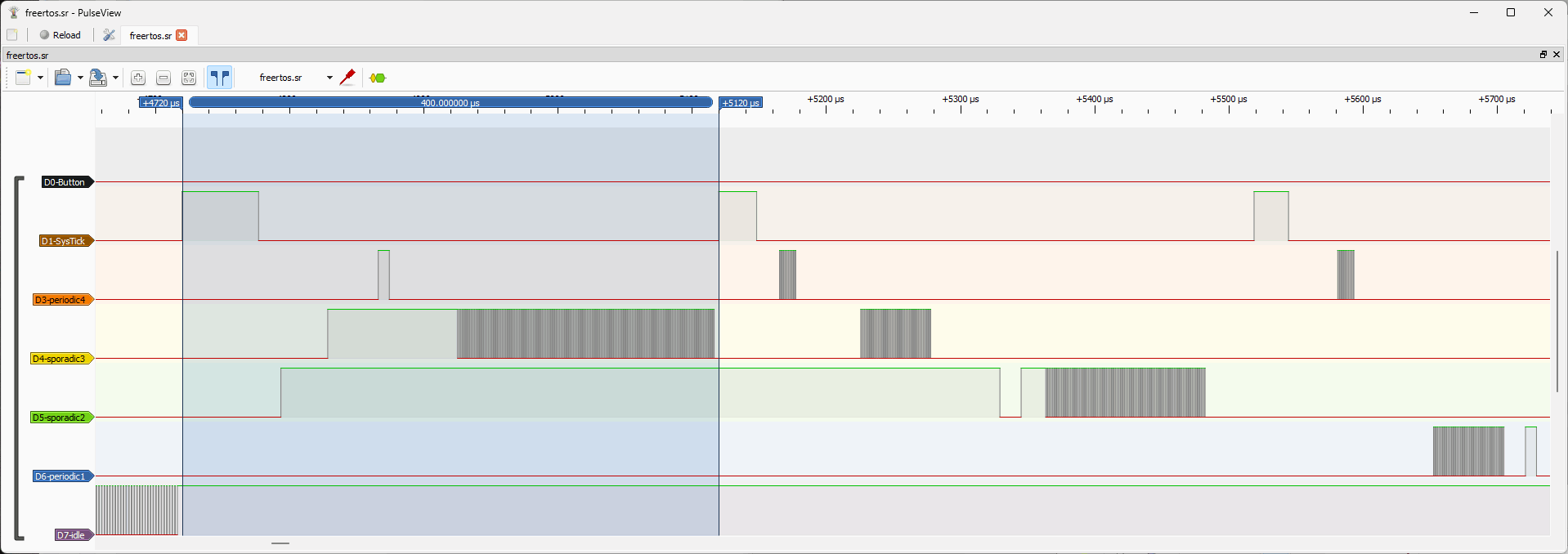

Logic analyzer trace after pressing the button (preemptive FreeRTOS kernel)